万物智能化时代如何实现指数级增长?软硬件结合是关键

万物智能化时代如何实现指数级增长?软硬件结合是关键美国时间5月16日,英特尔2019开源技术峰会(OSTS)在华盛顿州Stevenson圆满结束。大会从14日开始,共持续3天。在今

美国时间5月16日,英特尔2019开源技术峰会(OSTS)在华盛顿州Stevenson圆满结束。大会从14日开始,共持续3天。在今年的开源技术峰会上,英特尔公司高级副总裁兼架构、图形与软件部门总经理Raja Koduri发表“指数级思维”的演讲报告。他提出,如果想实现指数级的增长,必须要硬件和软件共同创新。软件社区和硬件社区相互交流,并真正去思考彼此的问题,比以往任何时候都更重要。

1000亿设备互通的下一个时代 软硬件如何结合

过去几年间大家所能获得的计算力正在以惊人的速率增长。计算力指数级上升的实现,正是基于硬件与软件的结合(Contract)。

回顾过去35到40年间计算的发展历程,计算力的增长速率呈指数级上升,从万物数字化、万物互联、万物移动化到万物云化,当前进入万物智能化。然而,Raja指出:“万物智能化不单是物联网(IoT),因为很多早期的IoT设备并没有那么智能,真正的万物智能化是能够真正帮助我们的智能设备。”

在PC时代,互联网用户增长了10亿人。硬件和软件结合的典型例子就是PC上X86架构和Windows系统的结合。

进入移动化时代,从10亿的互联网用户增长到100亿的设备,呈现10倍的增长,这些是硬件软件的结合发生了变化。变成了ARM架构和iOS及Android操作系统,同时Linux系统和X86平台也占据一部分市场。

当前,大家开始谈论1000亿台设备相互交流的下一个时代。Raja表示,无论是硬件、软件、操作系统还是相关技术,需要思考的一个问题是硬件和软件如何结合。什么可以替代Linux和X86,ARM和iOS、安卓,或者X86和Windows,支持这1000亿台设备呢?

除了密度之外,还有哪些创新来实现指数级增长

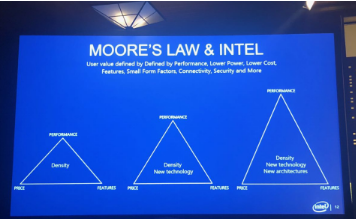

这种指数级的增长,与摩尔定律息息相关。摩尔定律是计算机革命的脉搏,现在关于摩尔定律有很多声音:将何去何从、摩尔定律已死等等。

摩尔定律描述的四个重要特征:晶体管密度、单价性能、每瓦性能、频率。

摩尔定律的发展大致分为三个时期:第一个时代是被称为黄金时期的兆赫时代,晶体管密度、单位性能和每瓦性能上都实现了极大提升,频率也在每两年大幅提升一次。第二个是多核时代,这期间晶体管密度继续增加,但是单位性能下滑了,每瓦性能从平均1.7倍降到1.3倍,频率也有所放缓。下一个时代是架构时代,内核会进一步扁平化,密度稍微低一些,但整体还是会像摩尔定律所说的每两年提升一次。每瓦性能会低一点,频率会低一点。

“如果想实现指数级的增长,那就必须要硬件和软件来共同创新。软件社区和硬件社区相互交流,并真正去思考彼此的问题,这比以往任何时候都更重要。” Raja强调,“不仅仅是实现晶体管的指数级增长。除了密度之外,还有哪些创新,来实现用户价值的指数级增长呢?”

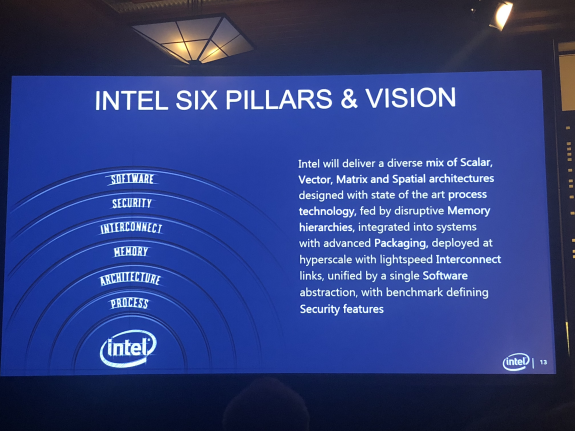

对此,Raja提到英特尔的最新策略:“英特尔将提供多样化的标量、矢量、矩阵和空间架构组合,以先进制程技术进行设计,由颠覆性内存层次结构提供支持,通过先进封装集成到系统中,使用光速互连进行超大规模部署,提供统一的软件开发接口以及安全功能。”Raja也表示,这里的英特尔其实适用于整个科技界。

同时,英特尔推出了六大技术支柱——软件、安全、互联、内存/存储、架构、制程/封装,围绕这六大技术支柱制定了技术和架构的路线图。

在制程方面,是晶体管、封装和设计的同步的联合架构优化,这三者需要紧密地结合在一起来推动摩尔定律继续发展。对于硬件领域的人来说,如果对比性能、功率和成本这三个方面,没有单个的芯片类型可以成为所有工作负载的最优解。对桌面CPU来说,最好的是能将频率提高到5GHz或以上的高性能CPU,但它对显卡、AI芯片或者FPGA、移动芯片来说却并不好,这就是问题关键所在。对此,英特尔制定的路线图是:用先进技术把不同的小芯片,甚至是不同的核连接起来。这样能让单片SOC实现性能、功耗和成本的最佳组合。

在封装方面,英特尔也制定了技术路线图。标准封装的接点间隔大约是110微米,然后到嵌入式多芯片互连桥接2D封装(EMIB)技术,它的接点间隔就是前者的一半,这样在二维中就可以得到更大的带宽,功耗也更低,能下降近1/5。

Foveros 3D封装技术,将是下一个技术飞跃。此外,就是为解决晶体管密度问题而开发的工具,从而在一个封装上构建完整的系统,集合不同速度的晶体管和IO芯片、互连等等。

“在制程和封装技术上,有密度的提升,有Foveros技术进步。进而利用先进的封装技术为每个工作负载都提供相应最优的芯片。”Raja讲道。

此外,在接下来的10年中,将会看到比过去50年中多得多的架构提升。

在架构方面,工作负载有多种。比如,看起来像标量计算的计算,像向量计算的计算,像矩阵计算的新型卷积计算,以及FPGA代表的空间架构。不同的工作负载好像是一片土地上的不同地区,中间被深沟隔开。“在接下来5-10年中,最重要的现代工作负载,就是这种标量、矢量、矩阵和空间架构的组合。”Raja强调。

对于每个架构而言,性能和通用性都很重要。CPU是最通用的,虽然可能不是其中性能最好的。GPU在性能模型上有些创新,但不像CPU那么通用,但是GPU对于高强度工作负载的性能更好。FPGA加速器效率要高得多,但并不通用。Raja指出:“真正需要关注的是性能和通用性的不同搭配组合。”

对此,英特尔的愿景和路线图是,提供标量、矢量、矩阵和空间的多种架构组合,部署在CPC、GPU、FPGA和加速器套件之中。

在内存和存储方面,当前需要指数级和先进的内存层级架构,以满足当前的计算需求。当内存容量以指数级速率增加时,内存的带宽却呈次线性增长。内存层级架构上,从高速缓存到硬盘,每个级别都应该是10倍的提升。对此,英特尔也在开发封装内存、持久内存和3D NAND等技术,以实现10倍的提升。现在是否能实现这个目标,取决于设定在硬件和软件边界的哪一边。如果不改变相应的软件架构,这些内存层级架构的10倍提升都无法转化为实际的工作负载提升。

下一个技术支柱是互连,包括片上互连、芯片间互连、系统级互连和数据中心级互连。每个层级的互连都在创新。英特尔从片上、封装内互连、处理器间互连、数据中心互连到无线互连等各方面都有投入。同时,还开放了Compute Express link(CXL)规范。Raja表示,这是英特尔的一项重大创举。

在安全方面,未来10年内任何成功的新架构都应将安全作为其基础和优先特性。安全的挑战源于外露面的指数级增长。6个内存层级架构,4个互连层级架构和数10亿个设备。在这其中,如果架构的每个部分都有1个指数级的外露面,那么需要保护4*6*4个面,即96的面。在业内,外露面仍然存在问题。每次向CPU添加新指令时,都会增加外露面。因此,对于所有硬件和软件方面来说,安全的挑战和机遇都是并存的。

最后一个支柱是软件。对于全新硬件架构的每一个数量级的性能提升潜力,软件能带来超过两个数量级的性能提升。

Raja指出:“英特尔在软件领域的策略是一个架构,像是CPU的图形架构,围绕架构进行扩展。我们拥有一个1200万活跃开发者的生态系统,横跨PC、网络和数据中心。”

同时,英特尔也设定三个目标。一是简便和可扩展。对于开发者来说,它应该易于使用,而且不仅可以扩展到所有的架构,更可以扩展到所有的操作系统,是从一个节点到生态系统中的数百万台互联设备。二是开放性,即将向所有人开放标准。三是必须提供统一的开发体验。“设定了这三个目标,特别是为了构建即将出现的计算机的异构性。”Raja表示。

为解决这个问题,英特尔投入一年多的时间在做OneAPI项目。One API整合了计算和架构创新,通过高速互连以及新的软件开发模式,为开发者简化API,并从英特尔计算架构释放出更高的性能和效率。Raja在大会现场正式宣布,One API项目将在2019年第四季度之前如期交付给开发者。

上一篇:百度不再效仿谷歌,否认分拆阿波罗

-

小米组织架构再调整,王川调职,雷军自任中国区总裁2019-05-28